RESULTS:

CCR Register Value: N/A

TRISE Register Value: N/A

Timing Register Value: N/A

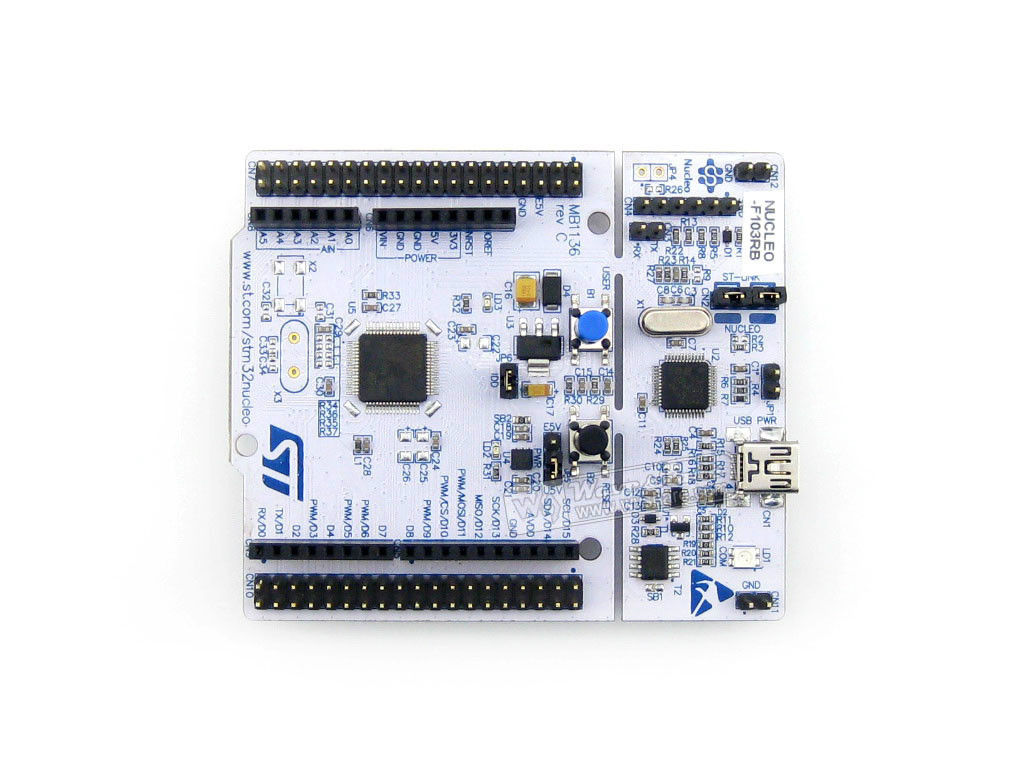

I2C (Inter-Integrated Circuit) is a widely used communication protocol in embedded systems, particularly in STM32 microcontrollers. Configuring the correct clock settings for I2C communication is crucial for reliable data transmission. However, calculating the necessary parameters, such as the Clock Control Register (CCR), the Rise Time Register (TRISE), and the Timing Register in newer STM32 versions, can be complex.

To simplify this process, we’ve developed an STM32 I2C Clock Calculator, which allows users to quickly determine the required settings based on the peripheral clock (PCLK) and the target I2C frequency.

Understanding I2C Clock Configuration

STM32 microcontrollers implement I2C timing configuration through different registers depending on the version:

- CCR (Clock Control Register): Determines the clock period based on the PCLK and the desired I2C frequency (older STM32 models).

- TRISE (Rise Time Register): Ensures that the SDA and SCL lines meet the required timing constraints for correct signal transitions.

- Timing Register: Used in newer STM32 microcontrollers (such as STM32F7, STM32H7, and STM32L4) to configure I2C timing more precisely.

I2C Modes in STM32

STM32 supports two primary I2C speed modes:

- Standard Mode (SM): Operates at a maximum of 100 kHz.

- Fast Mode (FM): Operates up to 400 kHz.

The formulas for computing CCR and TRISE values are as follows:

Standard Mode (≤ 100 kHz)

-

CCR = PCLK / (2 * Target Frequency) -

TRISE = (PCLK / 1,000,000) + 1

Fast Mode (≤ 400 kHz)

-

CCR = PCLK / (3 * Target Frequency) -

TRISE = (PCLK / 1,000,000) * 300 / 1000 + 1

For newer STM32 models, the Timing Register is used instead, requiring a more detailed calculation based on SCL timing constraints:

Timing Register Calculation (Newer STM32 Versions)

The Timing Register is composed of multiple fields:

- SCLL (Low period of SCL clock):

(PCLK / (2 * Target Frequency)) - 1 - SCLH (High period of SCL clock):

(PCLK / (2 * Target Frequency)) - 1 - SDADEL (Data hold time):

(PCLK / 100,000,000) (Approximate placeholder) - SCLDEL (Data setup time):

(PCLK / 50,000,000) (Approximate placeholder)

The final Timing Register Value is calculated as:

TIMING = (SCLDEL << 20) | (SDADEL << 16) | (SCLH << 8) | SCLL

Using the STM32 I2C Clock Calculator

This tool provides a user-friendly interface where you can:

- Select whether you are using an Older STM32 (CCR/TRISE) or Newer STM32 (Timing Register).

- Enter the Peripheral Clock (PCLK) in Hz.

- Specify the Target I2C Frequency in Hz.

- Click "Calculate" to obtain the necessary timing values.